강좌 & 팁

안녕하세요

이번 강좌에서는 파이프라인 등 버스 인터페이스에 대해 설명 하겠습니다.

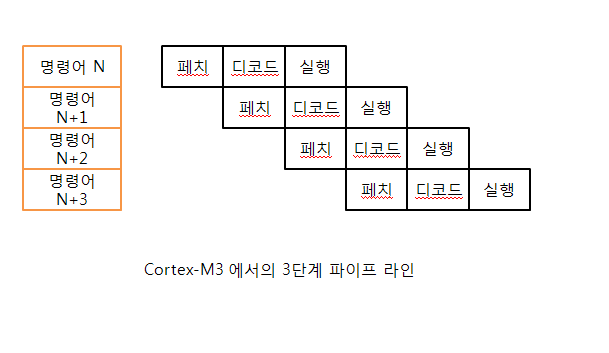

1.1 Cortex-M3 3단계 파이프라인

대부분 16비트 명령어들을 가지고 프로그램을 실행할 때 프로세서가 매 사이클마다 명령어들을 페치하는 것은 아니라는 점을

알게 될 것입니다. 이것은 프로세서가 한 번에 두 명령어씩 페치하기 때문입니다. 한 명령어가 페치된 후에는 바로 다음 명령어가 프로세서 내부에 위치하게되어 이런 경우에 프로세서 버스 인터페이스는 다음 명령어 뒤에 오는 명령어를 페치하려고 하며,

버퍼가 가득 차있다면 버스 인터페이스는 대기 상태가 됩니다. 일부 명령어를 실행하는 데에 있어서여러 사이클이 소요될수 있는데 이 경우 파이프라인은 중지 상태가 됩니다.

분기 명령어를 실행하는 경우 파이프라인은 플러시될 것입니다. 프로세서는 파이프라인을 다시 채우기 위해 분기 목적지에서

명령어를 페치해야 합니다. 하지만 Cortex=M3 프로세서는 v7-M아키텍쳐 안에 있는 많은 명령어들을 지원합니다.

프로세서의 파이프라인 특성과 프로그램 코드가 Thumb 코드와 호환된다는 것을 보장하고 있기 때문에 명령어 실행 동안에

프로그램 카운터를 읽으면 그 읽은 값은 주소에 4를 더한 값이 됩니다. 이 오프셋은 16비트 Thumb 명령어와 32비트 thumb-2

명령어의 조합과 독힙적인 상수 입니다.

프로세서 코어의 명령어 프리페치 장치 내부에는 명령어 버퍼도 있습니다.

이 버퍼는 추가적인 명령어들이 필요로 하기 전에 큐에 쌓일 수 있도록 해줍니다. 이 버퍼는 명령어 과정이 워드로 정렬되지

않은 32비트 Thumb-2 명령어를 포함하고 있을 때 중단되지 않게 해줍니다. 하지만 이 버퍼는 파이프라인에 추가단계를 덧붙이지

않기 때문에 분기 패널티를 증가시키지 않습니다.

2.1 Cortex-M3에서의 버스 인터페이스

Cortex-M3 프로세서를 사용하여 SoC 제품을 설계하고 있지 않다면 여기서 설명한 버스

인터페이스 신호에 직접 접근하는 것이 쉬운 일은 아닐 것입니다. 보통 칩 제조사들은 모든 버스 신호들을메모리 블록과

주변장치에 연결할 것입니다. 하지만 어떤 경우에는 칩 제조사들이 버스를 버스 브리지에 연결하고 외부 버스 시스템들을 칩 외부에 연결하기도 합니다. Cortex-M3 프로세서에서의 버스 인터페이스는 AHB-Lite 및 APB 프로토콜을 기반으로 하고 있는데, 이것은 AMBA Specification에 문서화되어 있습니다.

I-코드 버스

I-코드 버스는 0x00000000에서 0x1FFFFFFF 사이의 메모리 영역에서 명령어를 페치 하기 위해 사용되는 AHB-Lite 버스

프로토콜을 기반으로 하는 32비트 버스입니다. 명령어 페치는 Thumb 명령어일지라도 워드 크기로 수행 됩니다. 그러므로

실행하는 동안 CPU 코어는 한 번에 두 개의 Thumb 명령어를 페치할 수 있습니다.

D-코드 버스

프로세서 상에서 버스 인터페이스가 비정렬 전송을 정렬 전송으로 전환 하기 때문에 이 버스에서는 비정렬 전송을 사용할 수 없습니다. 그러므로 버스에 연결되어 있는 메모리와 같은 소자들은 오직 AHB-Lite정렬 정송만을 지원합니다.

시스템 버스

시스템 버스는 AHB-Lite 버스 프로토콜을 기반으로 하는 32비트 버스입니다. 0x20000000에서

0xDFFFFFFF 그리고 0xE0100000에서 0xFFFFFFFF의 메모리 범위에서 명령어 페치와 데이터 접근을 위해 사용할 수 있습니다.

D-코드 버스와 마찬가지로 모든 전송은 정렬되어 있습니다.

외부 전용 주변장치 버스

외부 PPB는 APB 버스 프로토콜을 기반으로 하는 32비트 버스 입니다. 이것은 0xE0040000에서 0xE00FFFFF의 메모리 범위에서 전용 주변장치 접근을 위해 만들어졌습니다. 하지만 APB 메모리의 어떤 부분은 TPIU, ETM, ROM 테이블을 위해 이미 사용되고 있기 때문에 이버스에서 추가적인 주변장치를 연결하기 위해 사용될 수 있는 메모리 영역은 0xE0042000에서 0xE00FF000뿐입니다.

이 버스에서의 전송은 워드 정렬되어 있습니다.

디버그 접근 포트 버스

디버그 포트 버스 인터페이스는 APB 규정의 개선된 버전을 기반으로 하는 32비트 버스 입니다. 이것은 SWJ-DP 또는 SW-DP와 같은 디버그 인터페이스 블록에 연결 되기 위해 만들어 졌습니다. 다른 목적을 위해서 이 버스를 사용하지 않도록 합니다.

3.1 Cortex-M3에서의 다른 인터페이스

Cortex-M3 프로세서는 다양한 목적을 위한 많은 다른 인터페이스를 가지고 있습니다.

이 신호는 실리콘 칩의 핀에서는 대부분이 SoC의 다양한 부분에 연결되어 있기는 하지만 사용되지 않기 때문에 찾아보기

힘듭니다.

밑에 기타 인터페이스 신호를 설명 하겠습니다.

신호의 그룹 기능

- 멀티프로세서 통신 다중 프로세서 사이에서의 간단한 태스크 동기화 신호

- 슬립 신호 전원 관리를 위한 슬립 상태

- 인터럽트 상태신호 ETM 동작 및 디버그 사용을 위한 인터럽트 동작 상태

- 리셋 요청 NVIC로부터의 리셋 요청 출력

- 락업2 및 정지 상태 프로세서 코어가 락업 상태 또는 정지 상태에 진입하였다는 것을 가리킨다.

- 엔디안 입력 코어가 리셋이 걸렸을 때

- ETM 인터페이스 명령어 트에스를 위해 임베디드 트레이스 매크로셀에 연결 한다.

● ITM의 ATB 인터페이스 진보된 트레이스 버스는 트레이스 데이터 전송을 위한 ARM의 CoreSight 디버그

아키텍처안에있는 버스 프로토콜 이며, Cortex-M3의 인스트루먼트 트레이스 매크로

셀로 부터의 트레이스 데이터출력을 제공하는데 이것은 데이터 트레이스 포트

인터페이스 장치에 연결되어 있습니다.

오늘의 강좌를 마치겠습니다. 끝까지 읽어주셔서 감사하고, 조언이나 틀린점이 있다면

댓글로 알려주시기 바랍니다^^