하드웨어

mcu 의 데이터버스를 이용해 입/출력 회로를 구성 할 경우 해당 어드레스를 어떻게 할당할지 고민 해야 합니다.

어드레스 할당을 어떻게 하고 회로 구성을 어떻게 하는지 한번 알아 보겠습니다.

FALINUX 에서 설계한 EM-S5PV210 모듈입니다.

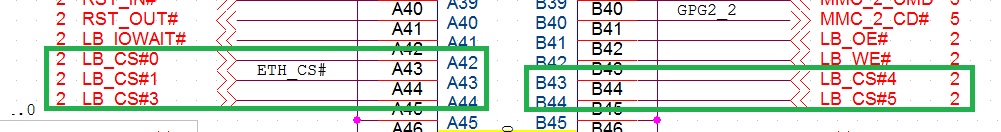

이 모듈에는 아래 회로도 와 같이 LB_CS#0 ~ LB_CS#5 까지 모두 연결 해서 사용 할 수 있도록 구성되어 있습니다.

cs 라는 것은 chip select 를 의미 하며, 각각의 cs 신호를 하나의 ic 에 할당 한다면 ... 몇개 쓰지도 못하겠지요.

그래서 cs 신호는 address 신호와 함께 구성해서 여러개의 cs 를 만들어 쓰게 됩니다.

그래서 개념적으로 메모리 상에 위치 하게 되는 것 입니다.

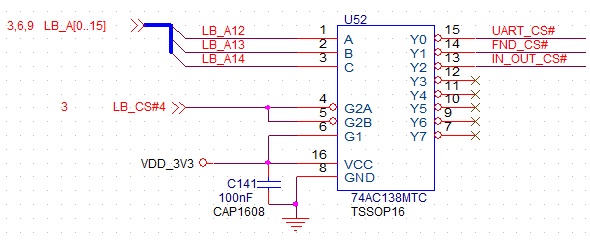

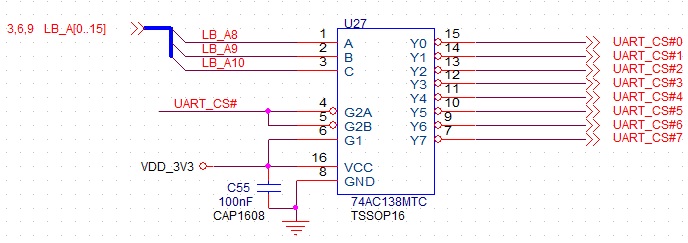

만약 아래와 같이 cs4 번을 이용해 여러개의 ic 들을 동작 시킬 수 있도록 회로를 구성 했다면 어드레스는 어떻게 될까요?

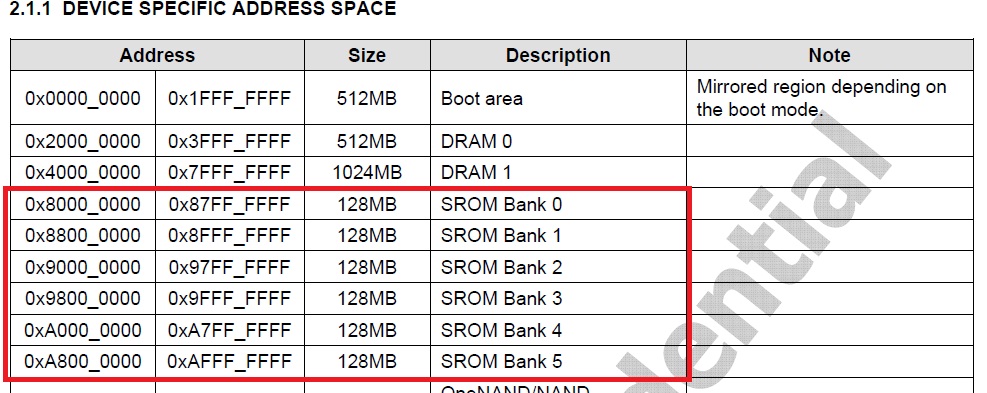

위 회로가 EM-S5PV210 모듈을 사용 하는 I/O 보드의 디코더 회로라면 S5PV210 데이터 시트의 메모리 맵을 확인해 보면

됩니다.

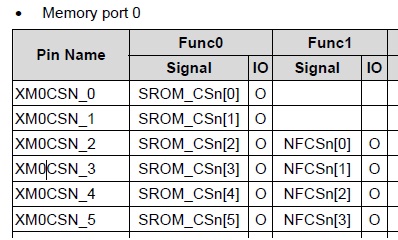

아래 그림을 보면 CS4 번은 SROM_CSn[4] 와 NFCSn2 두가지 기능을 하게 된다고 나와있군요.

이 말은 플래시 메모리르 사용 할 경우 이 CS4 가 NAND 플래시 CS2 번으로 사용 할 수 있다는 말입니다.

어쨋든 우리는 이 CS4 번을 사용 할 예정이고 메모리 위치를 보면 아래 그림과 같이 CS4 는 SROM Bank4 에 해당 하므로

0xA000 0000 ~ 0xA7FF FFFF 까지 128MB 의 영역을 갖고 있음을 알 수 있습니다.

즉, 어드레스 0XA000 0000 ~ 0XA7FFF FFFF 까지의 어드레스에 접근 하면 이 CS4 에 신호가 발생 된다는 말입니다.

그럼 저 위에 있는 디코더 회로는 어떻게 주소가 맵핑 될까요? 어드레스 12,13,14 번을 이용해 3x8 디코딩을 하므로 아래와 같이 맵핑 됩니다.

UART_CS# => 0xA000 0000

FND_CS# => 0xA000 1000

IN_OUT_CS# => 0xA000 2000

.

.

여기서 사용한 어드레스 12,13,14 는 설계자가 임의로 지정 한 것이긴 하지만, HEX 값으로 볼때 가장 쉽게 판단이 되는 숫자를 만들어 준 것입니다. 만약 12,13,14 가 아닌 15,14,13 을 할당 했다면. 0xA000 0000 , 0xA000 4000 ,0xA000 8000 .. 과 같이 살짝? 계산이 복잡해 집니다.

또한, 이렇게 만들어낸 CS 신호를 이용해 하위 어드레스 들과 조합해 더 확장 할 수 있으며, 위에서와 마찬가지로 가독성과 설계가 용이하도록 100,200,300 단위로 끊어지도록 A8,9,10 을 할당 해 줍니다.

이렇게 함으로써 CS4 는 8개의 CS 를 만들어 냈고, 그 8개중 하나를 이용해 또 8개의 CS 를 만들어 낼 수 있게 되었습니다.

그럼 이 어드레스는 어떻게 될까요.

0xA000 0000 -> UART_CS#0

0xA000 0100 -> UART_CS#1

0xA000 0200 -> UART_CS#2

0xA000 0300 -> UART_CS#3

0xA000 0400 -> UART_CS#4

0xA000 0500 -> UART_CS#5

이렇게 됩니다.

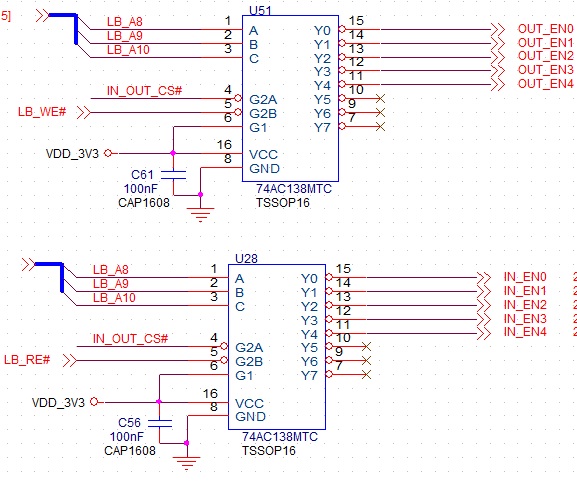

한가지 더 알아볼 것은. 만약 이렇게 많이 확장 하지 않고 최소로 IN/OUT 디바이스에 CS 를 할 당 하고 싶다면.

CS 신호와 ADDRESS 신호는 공통으로 주고, READ / WRITE 신호를 이용해 INPUT/ OUTPUT 을 구분 할 수 있습니다.

위 두개의 디코더는 동일한 주소를 갖지만 BUS 의 READ / WRITE 신호에 따라 출력이 달라집니다.

입력과 출력을 같은 어드레스로 할당 하기 때문에 개념적으로 하나의 장비를 통해 입/출력을 모두 하는 것 처럼 다뤄 질 수 있습니다.