강좌 & 팁

안녕하세요!

이번주는 익셉션에 대해 설명 하겠습니다.

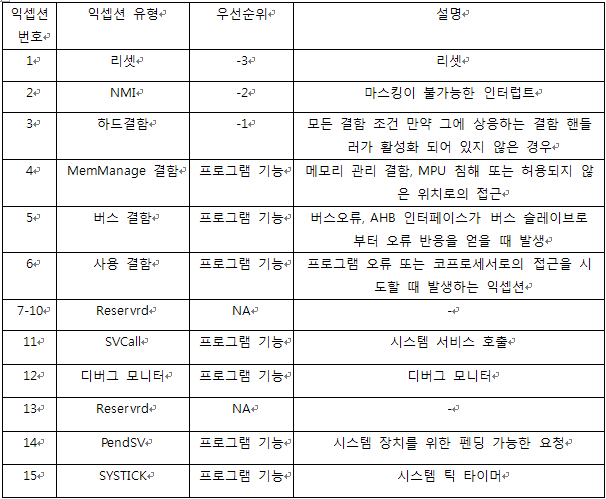

익셉션의 유형

Cortex-M3는 많은 시스템 익셉션과 외부 인터럽트들을 지원하는 특화된 익셉션 아키텍처를 제공하고 있습니다.

익셉션들은 시스템 익셉션을 위해 1~15번을 사용하고 있으며, 외부 인터럽트 입력을 위해 16과 그 이상의 번호를 사용합니다.

대부분의 익셉션들은 프로그램 사능한 우선순위를 가지고 있으며, 그 이상의 번호를 사용합니다. 대부분의 익셉션들은 프로그램 가능한 우선순위를 가지고 있으며, 몇 개는 고정된 우선순위를 갖습니다.

Cortex-M3 칩은 외부 인터럽트 입력(1~240)에 대해 그리고 우선순위 레벨에 대해 다른 번호들을 가질수 있습니다.

이것은 칩 설계자가 다른 요구 사항을 위해 Cortex-M3 설계 소스코드를 설정할 수 있기 때문입니다.

현재 실행되는 익셉션의 값은 특별한 레지스터 IPSR 또는 NVIC의 인터럽트 제어 상태 레지스터에서 규정할 수 있습니다.

여기서 인터럽트 번호는 Cortex-M3 NVIC로의 인터럽트 입력을 가리킨다는 것을 기억해 둬야 하며 실제 마이크로컨트롤러

제품 또는 SoC에서는 외부 인터럽트 입력 핀 번호가 NVIC상의 인터럽트 입력 번호와 일치하지 않을 수도 있습니다.

활성화된 익셉션이 발생하였지만 바로 수행되지 않을 때 그것은 펜딩될 것입니다. 이것은 익셉션이 수행될 수 있을 때까지

레지스터가 익셉션 요청을 저장하고 있을 것이라는 것을 의미 합니다. 이것은 전통적인 ARM 프로세서와는 다르며,

이전에 인터럽트를 발생시킨 장치들은 그것들이 처리될 때까지 그 요청을 저장하고 있어야만 했습니다.

이제는 NVIC안에 있는 펜딩 레지스터를 이용하여 인터럽트를 요청한 소스가 그 요청 신호를 삭제 한다고 하더라도 발생된

인터럽트가 처리될 수 있습니다.

우선순위 정의

Cortex-M3에서는 익셉션이 수행될지 여부와 언제 수행될지가 익셉션의 우선순위에의해 영향을 받을 수 있습니다. 더 높은 우선순위의 익셉션은 더 낮은 우선순위의 익셉션을 선점할 수 있습니다.

익셉션은 중첩된 익셉션/인터럽트 시나리오입니다. 어떤 익셉션들은 고정된 우선순위 레벨을 갖는데 그것들은 다른 익셉션보다 더 높은 우선순위 레벨을 갖는다는 것을 가리키기 위해 음수값을 갖습니다. 다른 익셉션들은 우선순위 레벨을 프로그래밍할 수 있습니다.

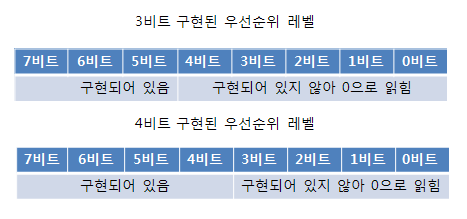

Cortex-M3는 3개의 고정된 최상위 우선순위 레벨과 256개 레벨의 프로그래밍 가능한 우선순위를 지원합니다. 하지만 대부분의 Cortex-M3 칩 또는 SoC가 설계될 대 설계자들은 원하는 레벨 번호를 얻기 위해 그것을 최적화합니다. 이렇게 레벨 수를 줄이는

것은 우선순위 설정 레지스터의 LSB 부분을 없앰으로써 구현할 수 있습니다.

MSB 대신 레지스터의 LSB를 제거하는 이유는 Cortex-M3 소자에서 다른 소자로 소프트웨어를 쉽게 포팅하기 위해서입니다.

이러한 방식으로 4비트 우선순위 설정 레지스터를 가지고 있는 소자를 위해 쓰여진 프로그램은 3비트 우선순위 배치를

반전해야 합니다.

우선순위 그룹이라고 불리는 NVIC에 있는 설정 레지스터를 사용하면, 프로그래밍 가능한 우선순위 레벨을 갖는 각각의 익셉션을 위한 우선순위-레벨 설정 레지스터는 반씩 두 부분으로 상위 절반은 선점형 우선순위이고, 하위 절반은 서브 우선순위입니다.

선점형 우선순위 레벨은 프로세서가 또 다른 인터럽트 핸들러를 이미 실행하고 있을 때, 인터럽트가 발생할지를 정의합니다.

서브 우선순위 레벨 값은 동일한 두 익셉션을 가진 선점형 우선순위 레벨을 동시에 발생할 때에만 사용됩니다. 이 경우 더 높은

서브 우선순위를 갖는 익셉션이 먼저 시행될 것입니다.

우선 순위를 그룹화한 결과 선점형 우선순위의 최대 폭은 7이며, 128개의 레벨이 있게 되는 것입니다. 우선순위 그룹이 7로 설정될 때 프로그래밍 가능한 우선순위 레벨을 갖는 모든 입셉션들은 동일한 레벨이 되며, 하드결함, NMI, 리셋을 제외한 이 익셉션들

간에 선점은 발생하지 않을 것입니다. 하드 결함, NMI, 리셋의 우선순위는 각각 -1,-2,-3이며 이것들은 이러한 익셉션들을 선점할 수 있습니다.

효과정인 선점형 우선순위 헤벨과 서브 우선순위 헤벨을 결정 할때 고려 해야할 점

● 구현된 우선순위-레벨 설정 레지스터

● 우선순위 그룹 설정

만약 Cortex-M3 소자가 우선순위-레벨 설정 레지스터 안에 있는 8비트를 모두 이용하여 구현되어 있다면, 0의 우선순위 그룹 설정을 사용하여, 그것이 가잘 수 있는 최대 선점형 레벨의 수는 128일 것입니다.

정확하게 동일한 선점형 우선순위 레벨과 서브 우선순위 레벨을 가지고 동시에 두 개의 인터럽트가 발생할 때, 더 작은 익셉션

번호를 갖는 인터럽트는 더 높은 우선순위를 갖습니다.

오늘의 설명은 여기서 마치겠습니다.

끝가지 읽어 주셔서 감사합니다.