하드웨어

글 수 321

2013.10.24 22:25:14 (*.52.177.249)

37553

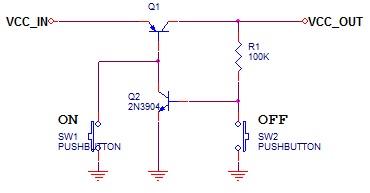

Tact Switch를 이용한 Power On/Off 를 Latch 하는 회로입니다.

이 회로도는 EEVBLOG(http://www.eevblog.com/)에 올라와 있는 회로도를 가지고 실험한 것입니다.

위 회로도는 SW1 Tact Switch(ON) 를 누르면 Q1이 Turn On 되어 전원이 공급되면 Q2가 Turn On 되어 전원 공급을 유지합니다.

SW2 Tact Switch(OFF) 를 누르면 Q2가 Turn Off 되고, Q1이 Turn Off 되어 전원 공급을 차단합니다.

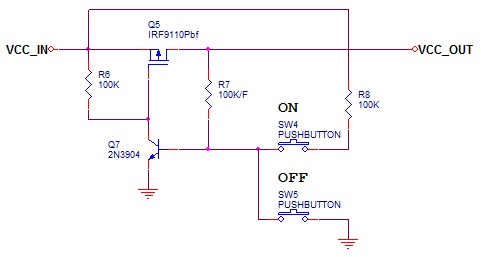

위 회로도는 MOSFET를 사용할 경우 SW4 Tact Switch(ON) 를 누르면 Q7 이 Turn On 되고, Q5 가 Turn On 되어 전원이 공급됩니다.

SW5 Tact Switch(OFF) 를 누르면 Q7 이 Turn Off 되고, Q5 가 Turn Off 되어 전원 공급이 차단됩니다.

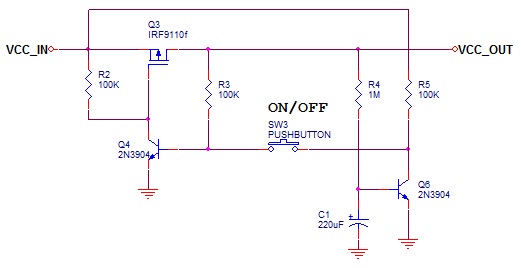

위 회로도는 MOSFET를 사용한 다른 방법으로 하나의 스위치로 ON/OFF를 할 경우에는 위의 회로도를 사용합니다.

이 회로도는 C1의 콘덴서값 또는 R4 의 저항값에 따라서 스위치의 채터링 방지 및 ON/OFF의 딜레이 시간을 설정할 수 있습니다.

실험 결과 만족할 만한 수준의 성능은 나오지 않습니다. 가끔 오동작을 하는 경우도 발생하는 것 같습니다.

좀더 수정 보안이 필요할 것 같습니다.