하드웨어

래치란 ?

래치(Latch)는 순차회로에서 한 비트의 정보를 저장 하는 회로입니다.

두 가지 상태의 입력 (Set, Reset) 에 따라 출력 상태(Q, Q') 를 가지며, nor 게이트를 이용하거나 nand 를 이용해 구성 할 수 있습니다.

------------------------------------------------------------------------------------------------------

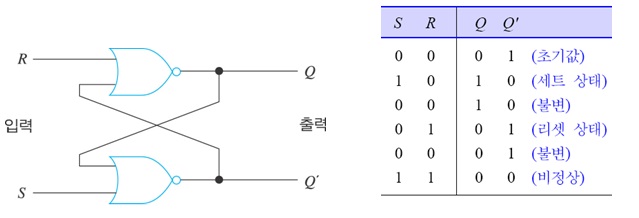

NOR 게이트를 이용한 SR 래치

입력 R과 S 의 상태에 따라 출력 Q,Q' 의 상태가 변하는 NOR 게이트를 이용한 SR 래치 입니다.

S,R 의 값이 모두 0 (low) 일때 출력 Q 의 상태가 변하지 않으며, 입력 S,R 이 서로 다를때

출력 Q 의 상태가 반전 됩니다.

------------------------------------------------------------------------------------------------------

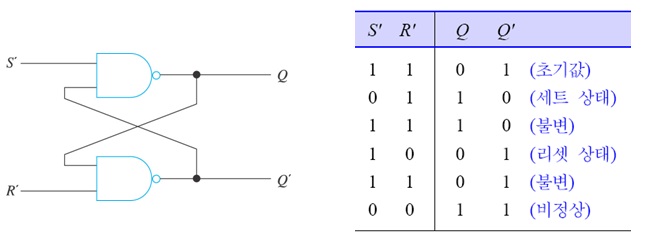

NAND 게이트를 이용한 SR래치

NOR 게이트를 이용한 SR 래치와 비슷 하지만 입력 S,R 의 상태가 NOR 게이트와 반대 임을 알 수 있습니다.

그래서 NAND 게이트를 이용한 SR 래치에서는 입력 S',R' 의 값이 모두 1 (High) 일때 출력 Q 의 값이 변경 되지않 습니다.

그런데 여기서 SR 래치의 기능상 문제점이 있습니다. 그 문제점은 타이밍 인데, 입력 S,R 이 언제 어떻게 입력이 될지

모른 다는 것이지요 그래서 현재의 입력에 대한 출력 상태를 확인할 타이밍을 정할 기준이 필요 합니다.

------------------------------------------------------------------------------------------------------

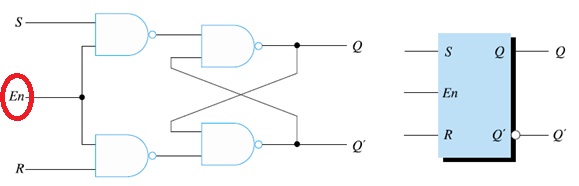

Enable 신호를 갖는 SR 래치

NAND 게이트를 이용한 래치에서 현재 입력 S,R 에 대한 출력만을 얻기 위해 En 신호를 추가한 형태 입니다.

En 신호가 0 (Low) 이면 첫번째 nand 게이트에 의해 입력 S,R 의 상태에 상관 없이 래치 입력이 모두 1 이 되며

출력 Q 의 상태는 변하지 않게 되는 것이지요,

즉 원하는 타이밍에 En 신호를 low 로 줌으로써 현재의 입력에 대한 출력 Q 의 값만을 얻을 수 있게 됩니다.

그런데.. 또 한가지 문제가 발견이 되었습니다.

그 문제는 입력 S,R 의 상태는 어떤 값이든지 허용 한다는 것이지요,

출력 Q,Q'의 값은 반드시 서로 반전된 값을 가져야 하는데. 만약 S,R 의 입력 상태가 모두 1 이고, En 신호가 high 라면

두 번재 nand 게이트의 입력이 모두 0 이 되어 출력 Q,Q' 의 값이 같아져 잘못된 출력 상태가 되는 것이죠.

결국 이 입력 S,R 의 상태는 같아서는 안되는 것이 되므로, 이를 해결한 것이 D-래치 입니다.

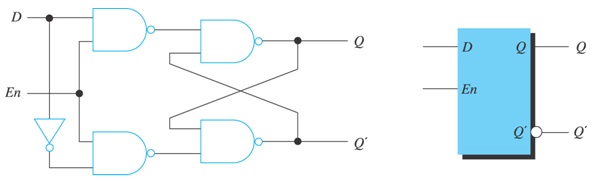

D래치

------------------------------------------------------------------------------------------------------

입력 S,R 대신 D 로 하고, 한쪽 입력은 D, 다른쪽 입력에 인버터를 사용해 반전 함으로써 서로 다른 상태의 입력을 만 들 수 있게 됩니다.

물론 래치만으로는 아직도 문제가 있습니다.

그 문제는 En 신호가 계속 해서 High 를 유지 했을 때 입력 상태가 변하면 출력 상태도 계속 해서 변한다는 문제점 입니다.

이 문제의 해결을 위해서 En 신호의 상태가 변하는 순간에만 현재의 입력이 출력에 적용 되도록 설계 합니다.

이것이 바로 플립플롭입니다.