안녕하세요. MAKUS 이우영 입니다.

오늘은 지난번에 만들었던 것들을 통합하여 boot.bin을 만들예정입니다.

ZYNQ를 구동하기위해 꼭 필요한 파일입니다.

하나씩 살펴보면 Bitstream 은 VIVADO에서 Generate Bitstream을 통해 나온 파일입니다.(~~.bit)

FSBL 은 First Stage Bootloader의 약자입니다. OCM 에서 동작을 시작해 시본적인 설정들을 초기화 해줍니다.

DDR도 여기서 설정을 해줍니다. 그 후 Bitstream 가 있다면 FPGA 부분을 활성화 해줍니다.

마지막으로 user application을 DDR 메모리에 복사하여 구동시켜 줍니다.

매우 중요하고 복작해 보이죠? 다행이도 SDK에서 자동으로 생성해 줍니다.!!

마지막으로 user application은 SDK에서 작성한 프로그램이나 U-boot.elf 를 뜻합니다.

이 3개의 파일을 하나로 만들면 boot.bin 이 됩니다.

이것도 SDK에서 가능합니다. 그럼 SDK를 실행해보겠습니다.

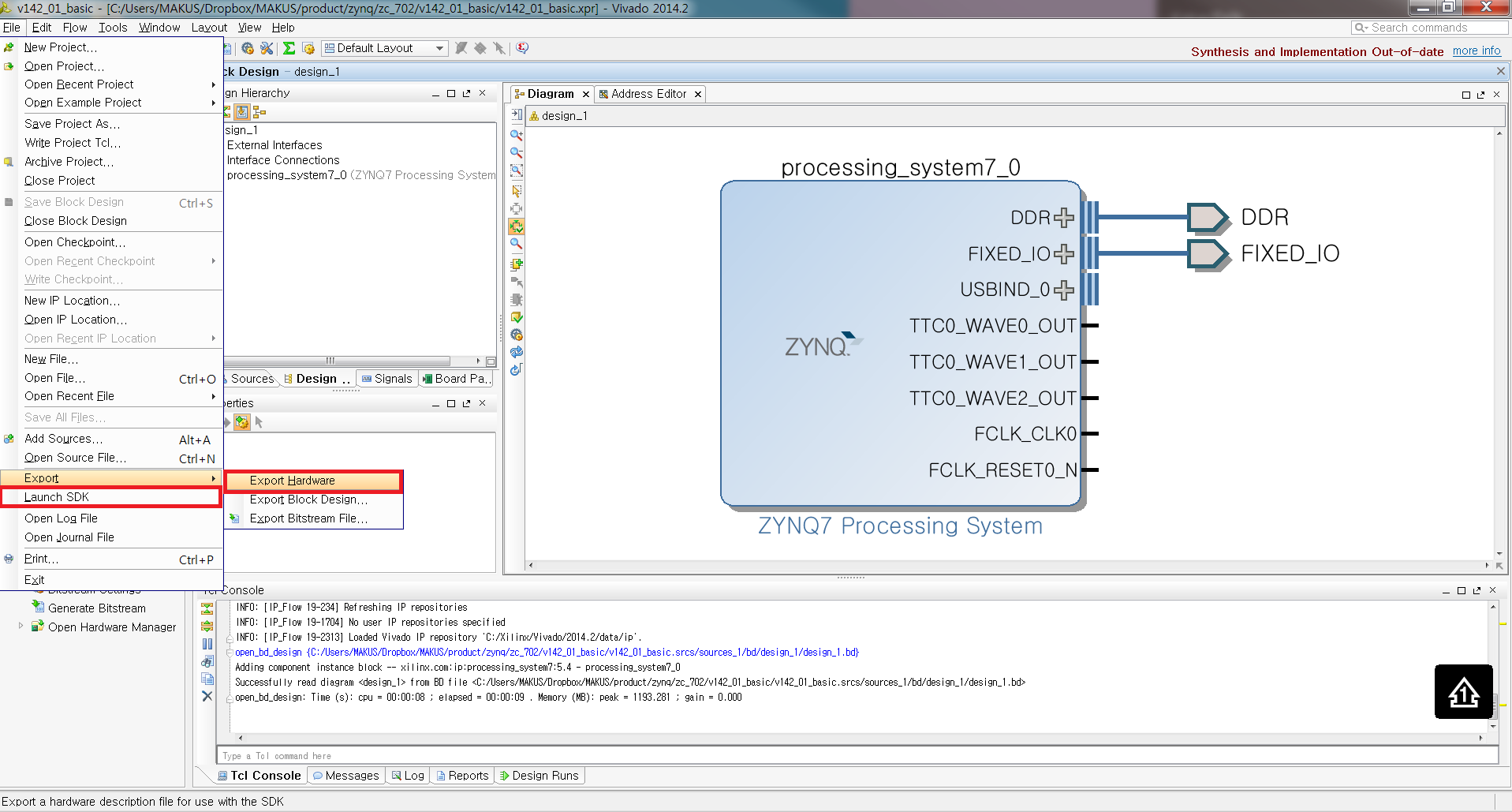

우선 전에 진행했던 VIVADO 프로젝트를 열어 줍니다. 그리고 Block Design을 열어줍니다.

그 후 다음 그림과 같이 Export Hardware 메뉴를 선택해 줍니다.

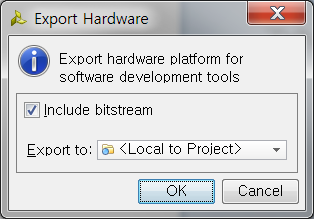

다음과 같이 include bitstream을 선택해 줍니다.

VIVADO 2014.1 이전 까지만 해도 이 메뉴에 Launch SDK 가 있었지만 2014.2 버전에는 따로 나와 있습니다.

file -> Launch SDK 메뉴를 선택해 주면 SDK가 실행 됩니다.

설정은 디폴트로 하는것이 편합니다. 그리고 Block Design이 열려있지 않다면 SDK가 실행되지 않을 수 있습니다.

SDK를 따로 실행해도 되지만 Block Design의 정보를 가져오기 위해서는 VIVADO를 통해서 실행하는것이 편합니다.

SDK는 요즘 많이 사용하는 eclipse 기반으로 만들어져 있습니다.

그러면 FSBL을 만들어 보겠습니다.

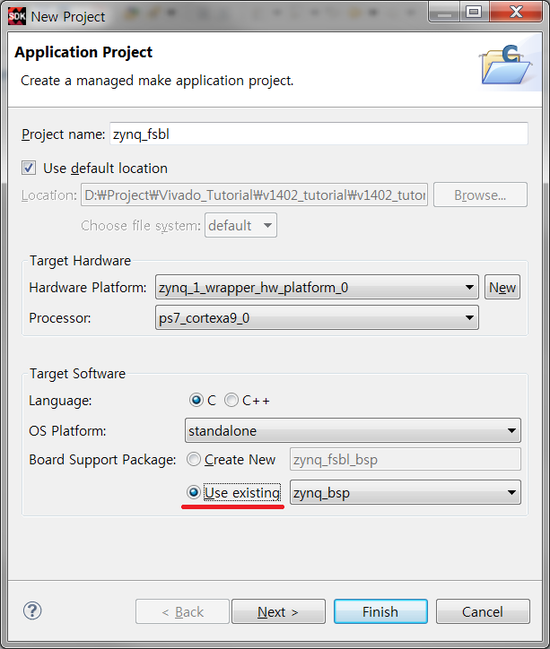

File -> New -> Application Project 를 선택해 주세요.

프로젝트 이름은 zynq_fsbl로 했습니다.

다른 설정은 필요없고 기존에 사용하던 BSP가 있다면 아래 그림처럼 선택해 주고 아니면 새로 생성해 줍니다.

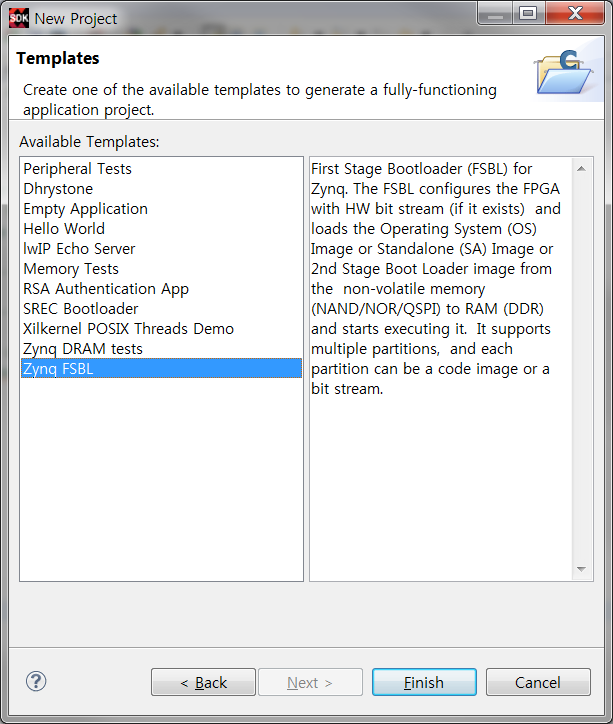

Next를 눌러 주면 다음과 같이 기본 템플릿을 제공합니다.

이중 Zynq FSBL이 있습니다. 이걸 선택하소 Finish를 눌러주면 FSBL이 생성됩니다.

간단하죠?

그러면 대충 필요한 파일들이 모였습니다.

FSBL은 오늘 만들었고 Bitstream은 첫번째 시간에 만들었습니다.

그리고 2번째 시간에 u-boot.elf 파일을 만들었었죠?

그럼 이것들을 가지고 BOOT.BIN 파일을 만들어 보겠습니다.

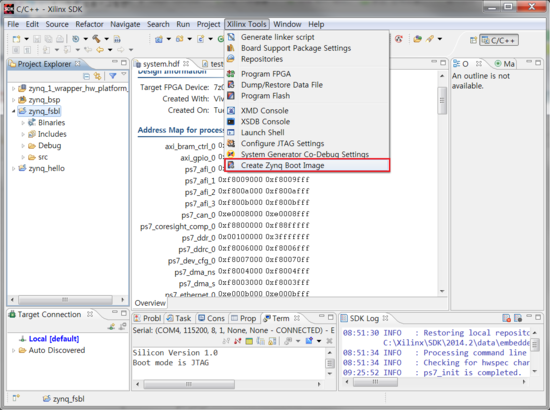

SDK에서 다음 그림과 같이 Create Zynq Boot Image 를 선택해 줍니다.

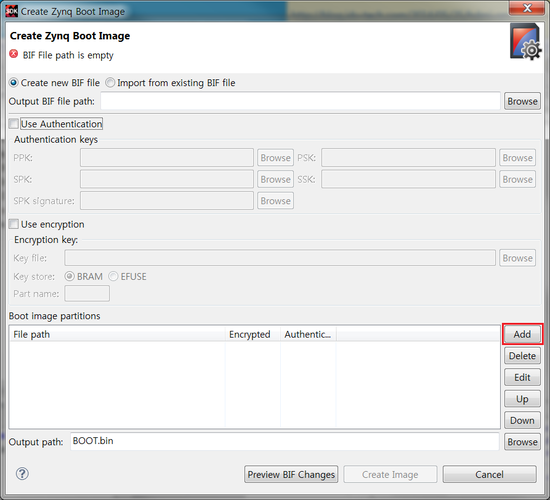

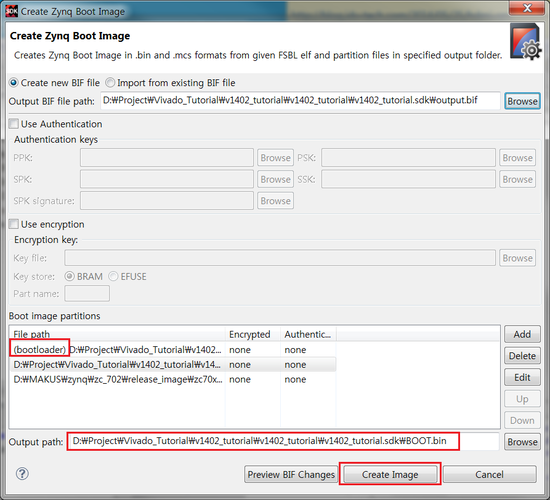

실행하시면 다음과 같은 화면이 나옵니다.

한번 boot.bin을 만들면 설정파일(BIF)을 저장하게 됩니다

이 설정파일이 저장되는 우치를 적당한곳에 설정을 해줍니다.

그리고 boot.bin에 들어갈 파일(FSBL.elf, bit파일, u-boot.elf)을 추가해야 합니다.

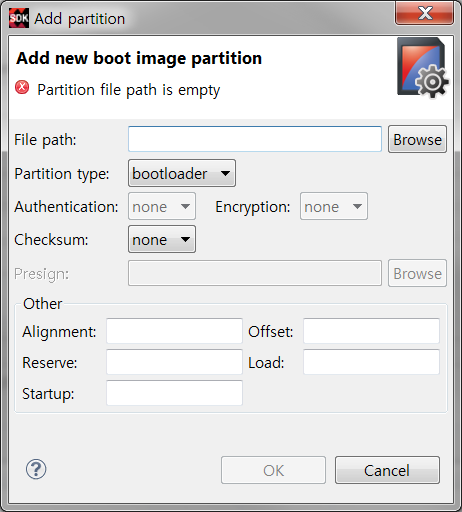

add를 누른 화면입니다.

먼저 FSBL.elf를 추가해 줍니다.

이때 FSBL은 type을 bootloader로 설정해 주어야 합니다.

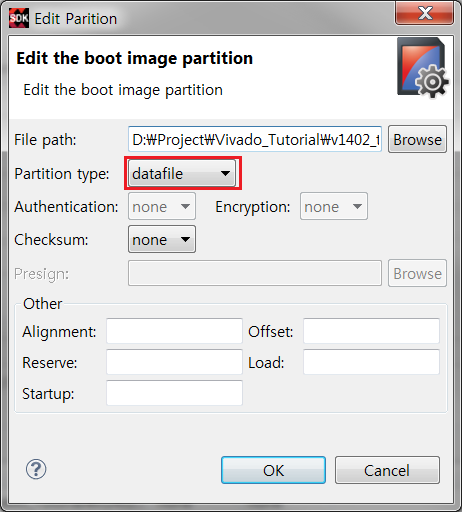

다음은 bit파일을 추가해 주겠습니다.

bit파일은 SDK를 실행할 때 같이 만들어지도록 설정을 해주었다면 hw_platform 폴더에들어있습니다.

사용자 설정에 따라 폴더이름이 변경됩니다. 저는 zynq_1_wrapper_hw_platform_0 폴더에

zynq_1_wrapper.bit라는 이름으로 생성되어 있었습니다.

이번에는 type을 datafile로 설정해 줍니다.

마지막으로 오늘 맨 처음 Xilinx 에서 받은 파일 중 u-boot.elf파일을 추가해 줍니다.

이 파일도 datafile 로 설정해 줍니다.

필요한 파일으 추가한 모습입니다.

아까 FSBL.elf만 설정이 다르기 때문에 나타나는 모습도 다른것을 볼 수 있습니다.

Output path를 설정해 주시고 Create Image를 누르면 Output path에 설정되 경로에 생성됩니다.

(경로에 파일명도 넣어주셔야 합니다.)

그럼 오늘은 여기서 마무리 하도록 하겠습니다.