하드웨어

몇년 전까지만 해도 RF관련 회로아닌 이상

PCB설계할때 RF효과에 대해 생각하지 않아도 되었습니다.

하지만 점차 MCU의 데이터 전송속도가 고속화되어

요즘은 RF효과를 전혀 고려 하지 않으면 회로가 제대로 동작않는 사태를 맞이 하게 되었죠

S3C6410 같은 고속의 MCU의 경우 가장 신경써야 될 부분이 있다면

MCU와 DDR의 아트웍 이라고 볼수 있겠습니다.

고속 데이터 전송이 이루어 지는 터라 패턴의 길이를 맞춰주고 임피던스 매칭을 잘해줘야 하죠

그래서

High speed PCB 설계 를 위한 Design guide를 몇개정도 뽑아 보았습니다.

1. Clock Line은 짧고 굵게 배선한다

길이가 길어질 경우 delay 문제가 발생

2 .Clock Driver, OSC 아래 부품배치 및 배선 금지

(Area Fill로 Ground 보강, 가능한 한 아래로 배선 금지)

3. 90도 배선 금지(45도는 괜찮음)

(Magnetic Field에 의한 Crosstalk를 줄인다)

4. Clock Line은 내층으로 배선하여 EMI를 감소시킨다

5. 고속 신호는 가능한 한 기판 중앙을 통하게 한다

(기판단 근처에 고속신호를 통하게 되면 GND면에 Common Noise 발생)

6. T 분기 금지의 원칙을 가능한 지킨다

(T분기시 Impedance mismatching 발생으로 신호 왜곡됨)

7. 고속 신호 Line에서는 가능한 한 Via사용을 줄인다

(Via에 의한 L,C 성분이 발생하여 Delay 및 Noise 발생)

8. GND는 가능한 한 Plane화 한다

(Plane 형태가 불가능 할 경우 Copper로 보강)

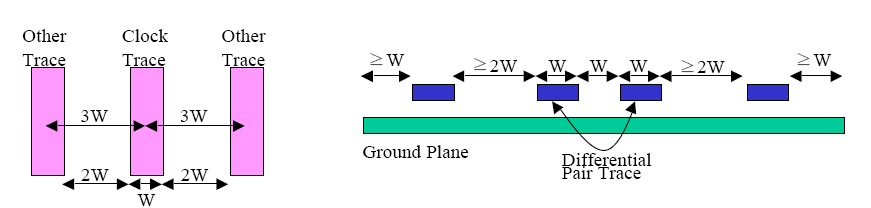

9. 3-W Rule 를 준수한다

Crosstalk를 최소화하기위해 Trace Width를 W라고할 때

Center to Center를 3W이상 이격(70% Flux Boundary)

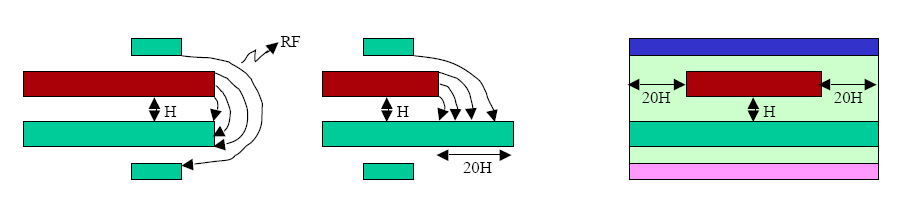

10. 20H-Rule 를 준수 한다.

High speed PCB에서 Power Plane Edge에서 RF Current

발생함. 이를 Fringing이라고 함

– Magnetic Flux Linkage에 의해 발생함

이를 최소화 하기위해 Power Plane은 가장 가까운

Ground Plane보다 두 층간 Gap을 H라고 할 때

20H만큼 작게 해 주어야 함

20H 규칙을 사용하면 PCB의 고유 자기 공진주파수가 상승한다.

11.고주파를 사용하는 신호선의 경우에는 그라운드를 커플로 만들어서 배선

(패턴은부드럽게회전하도록)

12.고속 신호선의 경우 배선길이를 맞추어 준다

배선의 길이가 맞지 않을 경우, delay time에 문제가 발생하고 동작이상으로 이어진다

이외에도 여러가지 룰들이 있지만 요정도만 조심해도 많은 개선(?)이 될것 같군요