강좌 & 팁

안녕 하세요.

이번주는 Cortex-M3의 개요에 대해 설명 하겠습니다.

1. Cortex-M3의 개요

앞에서 설명 했드시 cortex-M3는 32비트 프로세서 입니다.

32비트 프로세서는 32비트 데이터 경로와 32비트 레지스터 뱅크 인터페이스를 가지며 분리된 버스 인터페이스를 가지고 있기 때문에 8GB 이상의 메모리 공간을 가질 수 없습니다.

그래서 Cortex-M3는 복잡한 어플리케이션을 위해서 MPU를 사용하며 필요에 의해서 외부 캐시를 사용할 수 있으며 다양한 인터페이스들을 제공 합니다.

Cortex-M3는 R0~R15의 레지스터를 갖습니다. R0~R12까지는 데이터 동작을 위한 32비트 범용 레지스터 입니다.

16비트 Thumb 명령어들은 R0~R7까지만 접근이 가능 합니다.

R13은 스택 포인터이며 MSP(메인 스텍 포인터)와 PSP(프로세서 스택 포인터)가 있습니다.

MSP는 디폴트 스택 포인터 OS 커널과 익셉션 핸들러에 의해 사용됩니다.

PSP는 사용자 사용자 어플리케이션 코드에 의해 사용됩니다. 즉, 스택 포인터의 최하위 두 비트는 항상 0인데,

그것들이 항상 워드 정렬 되어있는 것을 의미 합니다.

R14는 서브루틴이 호출될 때 리천 주소가 링크 레지서트에 저장되는 링크 레지스터 입니다.

R15는 프로그램을 흐름 제어를 위해 쓰여지는 프로그램 카운터 입니다

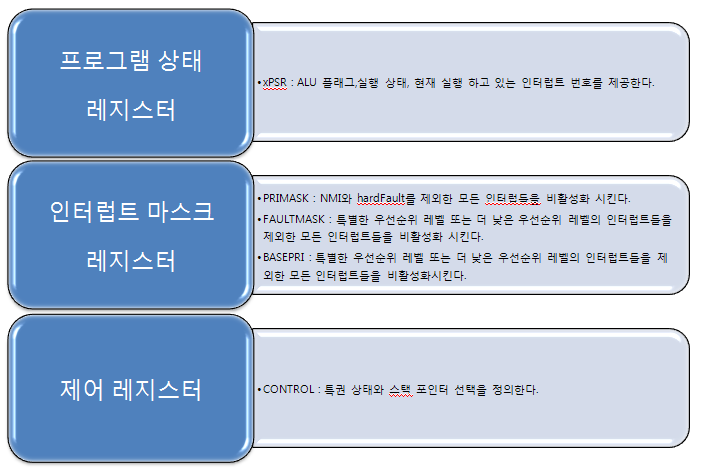

이외에도 Cortex-M3는 프로그램 상태 레지스터, 인터럽트 마스크 레지스터, 제어 레지스터의 특별한 레지스터들이 있습니다.

(특별한 레지스터)

2. 동작모드

Cortex-M3는 두 개의 모드와 두 개의 특권 레벨을 가지고 있습니다.

동작모드로는 operation mode, 쓰레드 모드와 핸들러 모드 입니다. 이 동작 모드는 프로세서가 보통의 프로그램을 실행하고 있는지 아니면 인터럽트 핸들러나 시스템 익셉션 핸들러와 같은 익셉션 핸들러를 실행하고 있는 지를 결정합니다.

특권 레벨은 privilege levels, 특권 레벨과 사용자 레벨이 있습니다.

특권 레벨은 기본적인 보호 모델을 제공할 뿐 아니라 크리티컬한 영역으로의 메모리 접근을 보호하기 위한 메커니즘을 제공 합니다.

프로세서는 쓰레드 모드를 실행하고 있을 때 특권 상태 또는 사용자 상태 중 하나에 있을 수 있습니다. 하지만 익셉션 핸들러 특권 상태 안에만 있을 수 있습니다.

프로세서가 리셋에서 벗어날 때, 그것은 특권 접근 권한을 가지고 쓰레드 모드 안에 있게 됩니다.

특권 상태 안에 프로그램은 모든 메모리 범주로 접근이 가능하며, 지원되는 모든 명령어를 사용할 수 있습니다.

특권 접근 레벨 안에 있는 소프트웨어는 제어 레지스터를 사용하여 프로그램을 사용자 접근 레벨로 전환할 수 있습니다. 익셉션이 발생하면 프로세서는 항상 특권 상태로 되돌아가며, 익셉션 핸들러에서 나올 때 이전의 상태로 되돌아갈 수 없다. 쓰레드 모드로 되돌아갈 때 프로세서는 특권 접근 레벨로 되돌리기 위해 제어 레지스터를 프로그래밍하는 익셉션 핸들러를 수행해야 합니다.

특권 레벨과 사용자 레벨을 분리한 것은, 신뢰성이 없는 일부 프로그램에 의해 시스템설정 레지스터들이 접근되거나 변경 되지 못하게 함으로써 시스템의 안정성을 향상시키게 됩니다.

내장된 중첩 벡터 인터럽트 컨트롤러 Cortex-M3 프로세서는 중첩 벡터 인터럽트 컨트롤러라고 불리는 인터럽트를 포함하고 있습니다.

- 중첩 인터럽트 지원

NVIC는 중첩 인터럽트를 지원하며 모든 외부 인터럽트들과 대부분의 시스템 익셉션들은 다른 우선 순위 레벨로 프로그램될 수 있습니다. 인터럽트 발생시 NVIC는 인터럽드의 우선순위와 현재 실행하고 있는 우선순위 레벨을 비교합니다. 새로운 인터럽트가 현재보다 레벨이 높으면 새로운 인터럽트의 인터럽트 핸들러는 현재 실행하고 있는 테스크보다 우선적으로 실행 됩니다. - 벡터 인터럽트 지원

Cortex-M3는 인터럽트가 걸리면 인터럽트 서비스 루틴의 시작 주소는 메모리의 벡터 테이블에 위치하게 됩니다. 그렇게 되므로 인터럽트 요청 시간이 적게 걸리는 것 입니다 - 동적 우선순위 변경 지원

인터럽트들의 우선순위 레벨은 런타임 동안 소프트웨어에 의해 변경될 수 있습니다.

서비스될 인터럽터 들은 그 인터럽트 서비스 루틴이 완료될 때까지 활성화로부터 블록이 됩니다. - 인터럽트 지연시간 감소

Cortex-M3 프로세서는 일부 레지스터 내용들을 자동으로 저장하고 복원하는 작업과 한 서브스 루틴에서 다른 서비스 루틴으로 전환할 때 지연시간을 줄여줍니다. - 인터럽트 마스킹

인터럽트와 시스템 익셉션은 우선순위 레벨 기반으로 마스킹되거나 인터럽트 마스크 레지스터를 사용하여 크리티컬한 태스크가 인터럽트 없이 제시간 안에 완료될 수 있도록 보장하기 위해서 사용합니다.

3.버스 인터페이스

- 코드 메모리 버스 : 물리적으로 두개의 버스로 구성됨

- 시스템 버스 : 메모리와 주변 장치로 접근하기 위해 사용됨

- 전용 주변장치 버스 : 디버깅 컴포넌트들과 같은 전용 주변장치를 위해 할당된 일부 시스템 레벨 메모리에 접근할 수 있게 해줌

4. 메모리 보호 장치

MPU는 다양한 방법으로 사용됩니다. 일반적인 시나리오에서 MPU는 운영체제에 의해 셋업되는데특권 코드에 의해 사용되는 데이터가 신뢰성 없는 사용자가 프로그램으로부터 보호될 수 있도록 해줍니다.

5. 디버깅 지원

-

JTAG 또는 시리얼-와아어 디버그 인터페이스 지원 합니다.

-

TM은 테스트 코드에서 디버그 정보를 출력하기 위한 간단한 사용방법을 제공합니다.

-

CoreSight 디버깅 솔루션 기반: 코어가 동작할 때조차 프로세서 상세 내용이나 메모리 내용에 접근이 가능합니다.

-

6개의 브레이크포인트와 4개의 와치포인트를 위한 기원 내장

-

DWT를 사용하는 명령어 트레이스와 데이터 트레이스를 위한 추가적인 ETM

-

디버깅을 더 쉽게 만들어 주기 위한, 결함 상태 레지스터들을 포함한 새로운 디버깅

-

DWT 내부의 PC 샘플러와 카운터들은 코드-프로파일링 정보를 제공합니다.

오늘은 여기서 끝내도록 하겠습니다.

부족한 점이 있으면 댓글로 말씀해 주시고

끝까지 읽어주셔서 감사합니다:))