강좌 & 팁

CPLD 에 VHDL 을 이용해 여러가지 로직을 구현 합니다.

이때 사용되는 툴이 ISE 입니다. 자일링스 에서 공개하는 툴입니다.

막상 설치 하고 보면 어떻게 사용 해야 하는지 난감하지요 저도 그랬습니다.

그래서 시작부터 프로젝트 생성, 컴파일 JTAG으로 퓨징하는것까지 설명해 볼까 합니다.

환경 : 이미 설치가 돼 있고,JTAG 까지 준비가 된 것으로 봅니다.

사용할 CPLD 는 XC95144XL입니다.

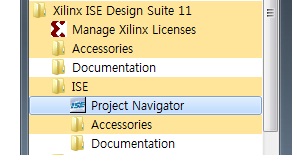

1. 실행

설치가 되면 윈도우 시작 버튼에서 아래 그림대로 찾아가면 Project Navigator 가 있습니다.

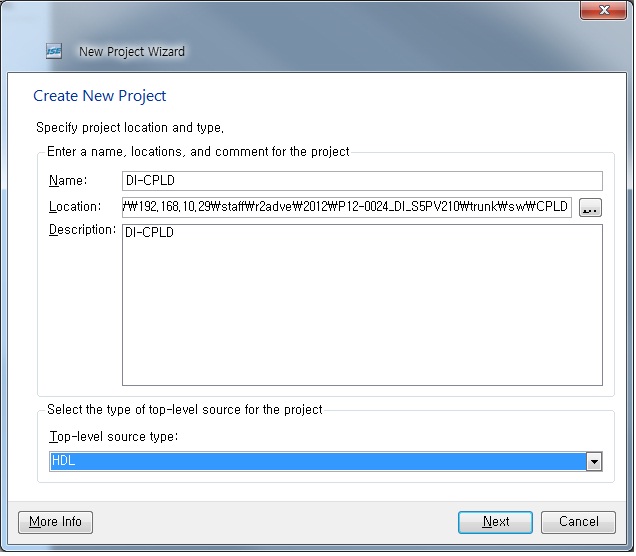

2. 프로젝트 생성 하기.

화면의 좌측 맨상단의 file - new project를 선택 하면 아래와 같은 화면이 나옵니다.

프로젝트 이름을 넣고, 저장할 경로를 선택 합니다.

아래 top-level source type: 에서 HDL 을 선택하고 NEXT 를 눌러줍니다.

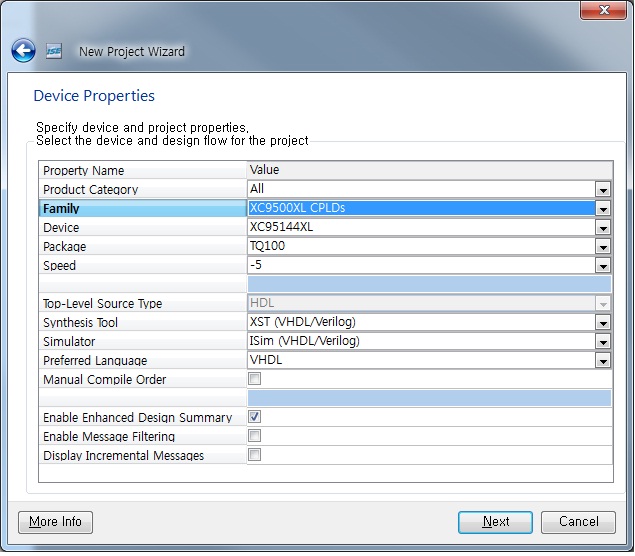

3. 환경 설정

그럼 사용할 CHIP 과 툴들을 선택 하는 화면이 나오며, 아래 와 같이 설정해 줍니다.

물론 XC95144XL-100PIN 을 사용 하지 않고 다른 칩을 사용 한다면 당연히 그 칩을 선택 해 주어야 겠지요.

]

]

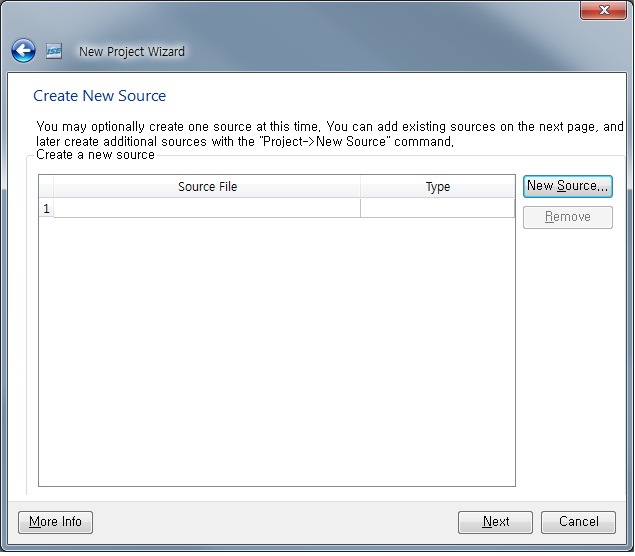

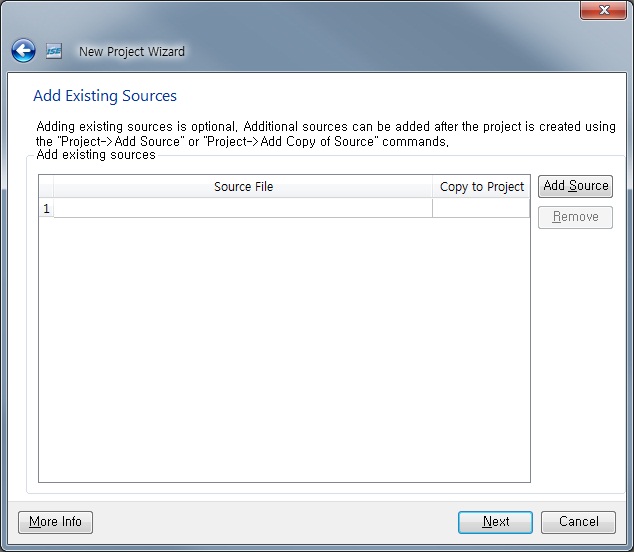

4. 소스파일 선택

이 화면에서 새로운 소스파일을 생성 할 수 있긴 하지만 나주에 추가가 가능 하므로 그냥 NEX 를 눌러줍니다.

5. 기존의 소스파일을 추가 할 수 있겠지만 물로 나중에 또 추가가 가능 하므로 역시 NEXT 를 눌러 줍니다.

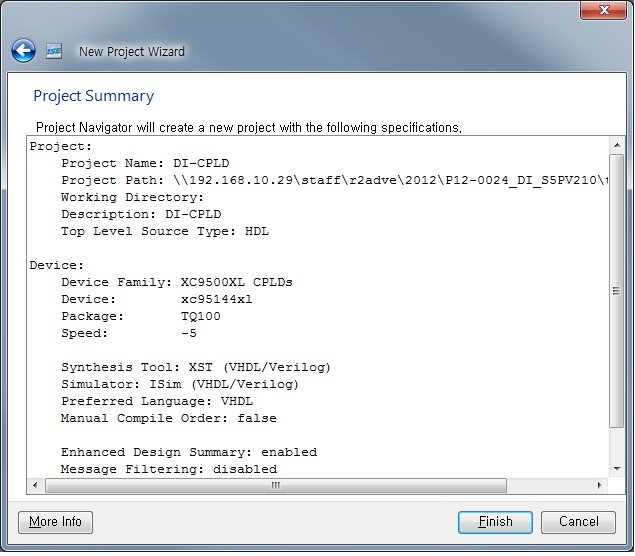

6. 프로젝트 환경 확인

지금까지 설정한 내용이 맞는지 확인 하는 화면이 나오네요 당연히 확인후 Finish 를 눌러 줍니다.

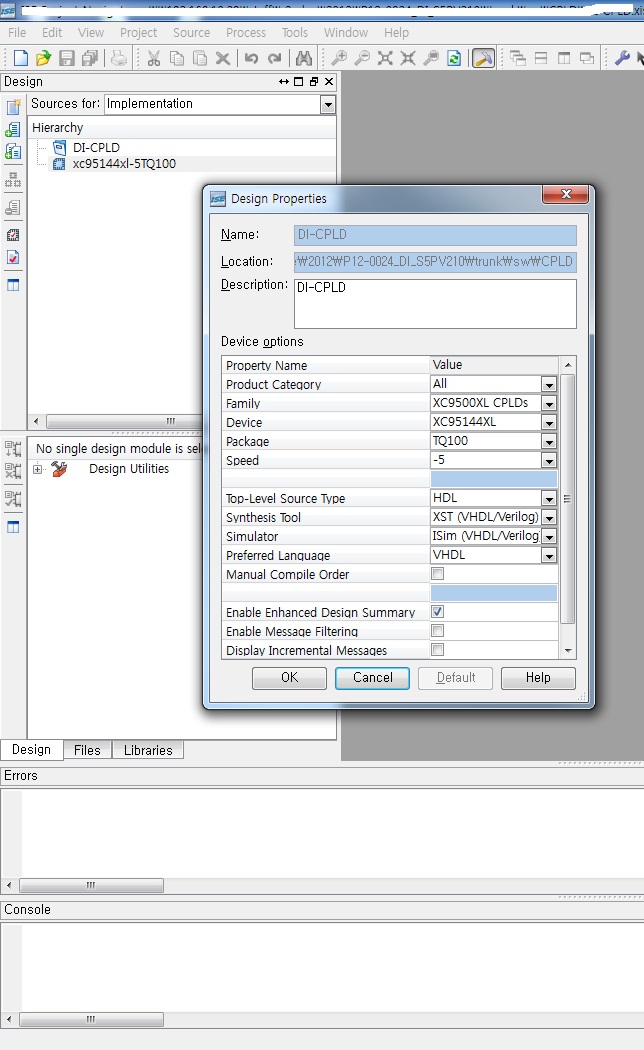

7. 환경 확인

프로젝트가 생성되면 아래 그림과 같이 작업 공간들이 나오는데요, 먼저 진행한 환경 설정이 잘못됐을 경우 아래 그림과 같이

선택된 chip 이름을 더블클릭 하면 properties 화면이 나오며 수정이 가능 합니다

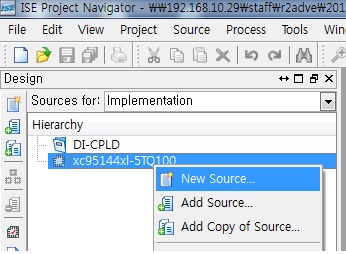

8. 소스파일 생성하기

칩 이름을 선택하고 마우스 우측 버튼을 누르면 새로운 소스 파일을 생성 할 수 있습니다.

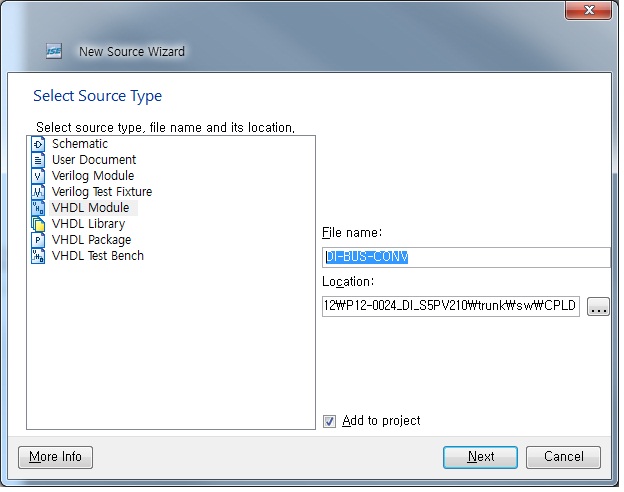

9. 생성할 소스파일 설정 하기

우리는 VHDL 을 사용할 예정이므로 VHDL Module 을 선택 하고, 적당한 파일 이름을 적어줍니다.

저장 위치는 현재 프로젝트가 생성된 위치가 기본적으로 잡혀 있으니 그냥 둡니다.

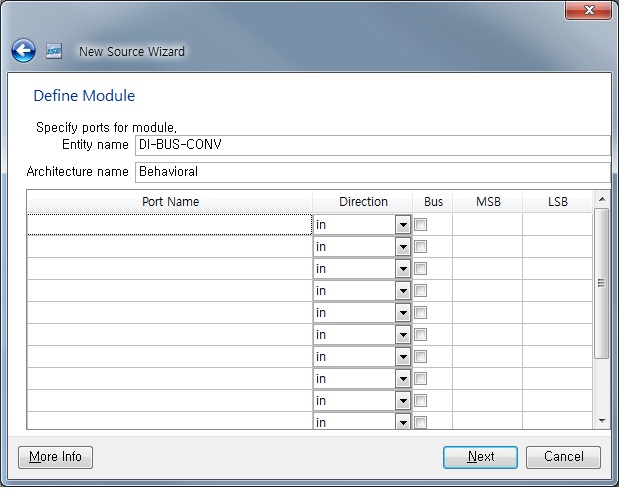

10. 파일 내용 구성 ( chip 에 따라 port 의 설정을 할 수있으며, 자동으로 소스화 됩니다.)

이곳에서 사용할 pin 들의 입출력을 선택 할 수 있으나, 이부분은 나중에 할 수 있으니 그냥 넘어 갑니다.

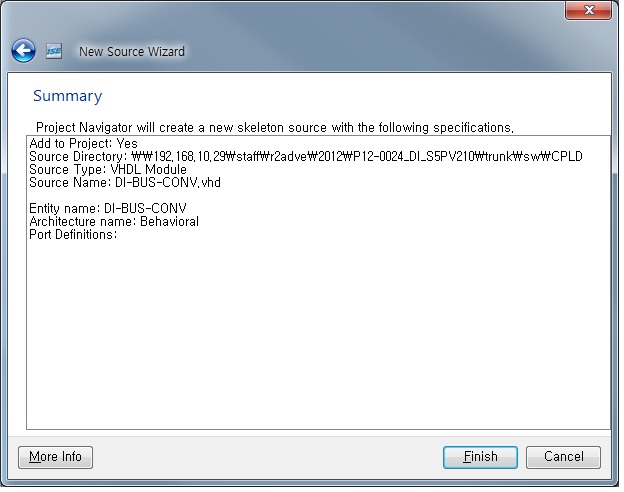

11.내용이 맞는지 확인 하고 finish 를 눌러줍니다.

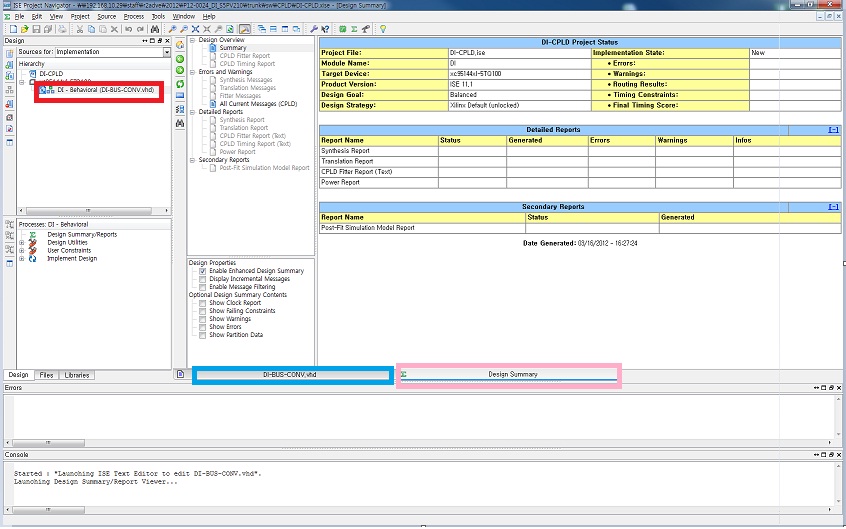

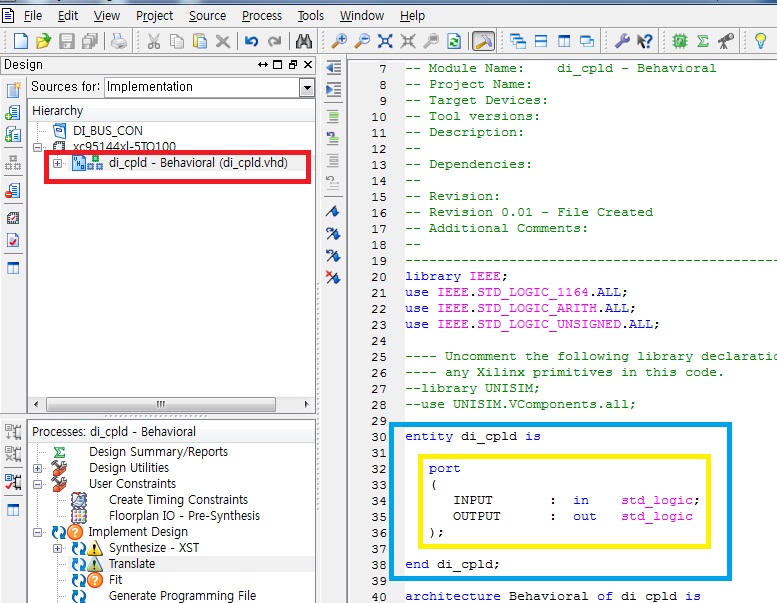

12. 파일생성 완료

소스파일이 생성되면 아래 그림의 빨간 네모처럼 xxx.vhd 파일이 생성됩니다.

vhd 파일은 프로젝트가 생성된 위치에 있으며 다른 에디터로 직접 수정이 가능 합니다.

파란 내모는 현재 열려있는 파일이고, 분홍색 네모는 프로젝트 환경을 나타냅니다.

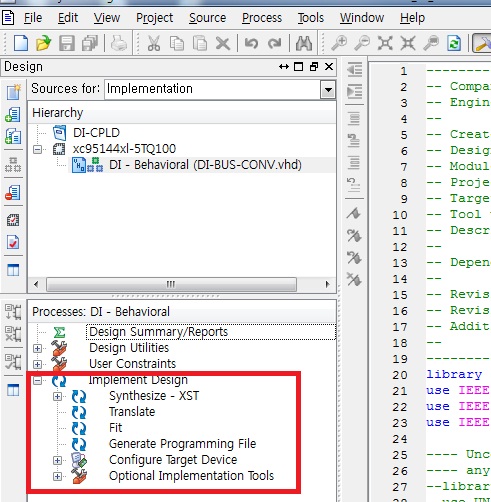

13. 컴파일

아래 그림의 빨간색 네모 부분이 실제 소스코드의 컴파일 단계를 말하며, 부분별로 또는 범위, 전체 컴파일 이가능 합니다.

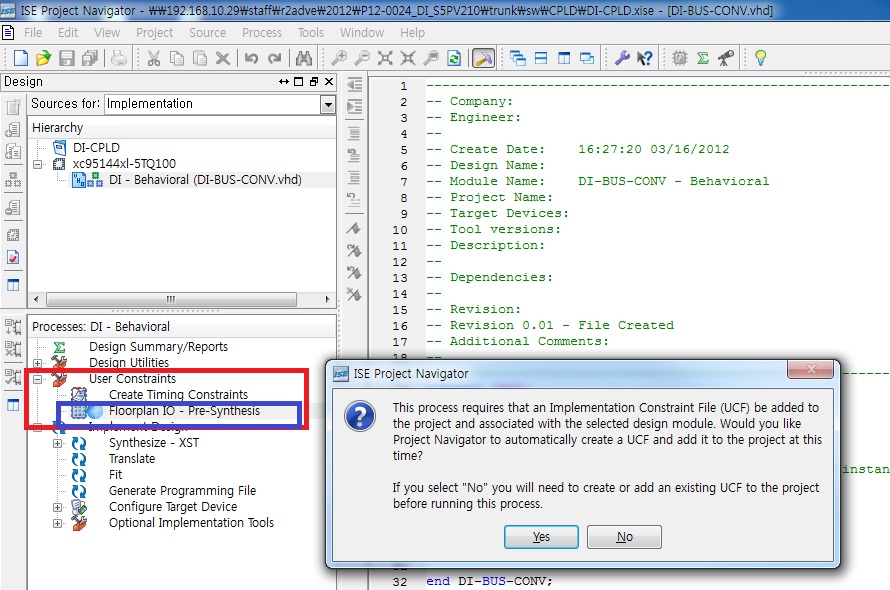

14. pin 매핑 하기

실제 vhdl 소스는 다른 chip 에서도 사용이 가능한 형태입니다. 다시 말해 실제 chip 과 매핑은 따로 한다는 말이지요.

그래서 실제 사용할 chip 의 pin 과 신호들을 매핑 시키는 작업을 해 주어야 합니다.

화면의 붉은색 네모상자안의 파란색 네모를 더블 클릭 합니다.

그럼 일단 yes 를 누르고 확인 합니다.

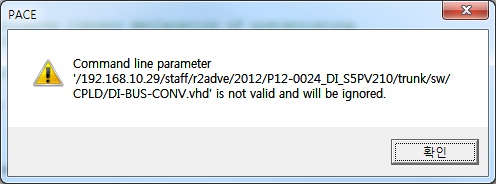

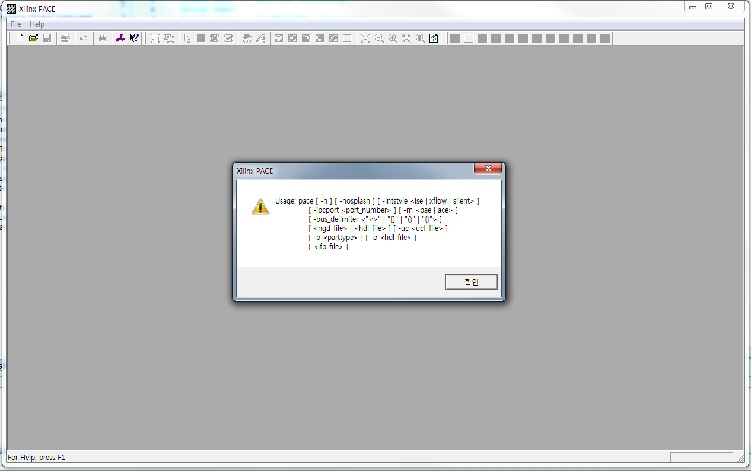

14. 주의 사항

13번 항목을 그대로 해보면 아래 그림과 같이 경고 메시지가 나오고 원하는 pin 매핑 화면이 나오지 않습니다.

이유는 몇 가지가 있겠으나 제 경험상 세 가지가 있는데요, 하나는 프로젝트 생성경로에 한글이나 특수문자 가 들어 갈때 이고,

또하나는 네트워크 상의 서버에서 프로젝트를 생성할경우 입니다. ( 이경우는 정확히 이해가 안갑니다만.. )

마지막으로 vhdl 코드에 매핑할 pin 을 하나도 정의 하지 않았을 경우 입니다.

15. pin 선언 하기

14번에서 언급한 세가지 오류 조건중 1,2 번째는 그냥 할 수있으니 넘어가고, 세번째인 pin 선언을 간단히 해보겠습니다.

먼저 생성한 vhd 파일을 더블클릭해 열어보면 맨위에 라이브러리 추가항목이 있고 그 아래 entity 항목이 나옵니다.

이부분이 pin 을 선언 하는 부분이며 , 간단히 그림의 파란색 내용과 같이 입력해 줍니다.

(문법적인 부분은 설명 하지 않습니다.)

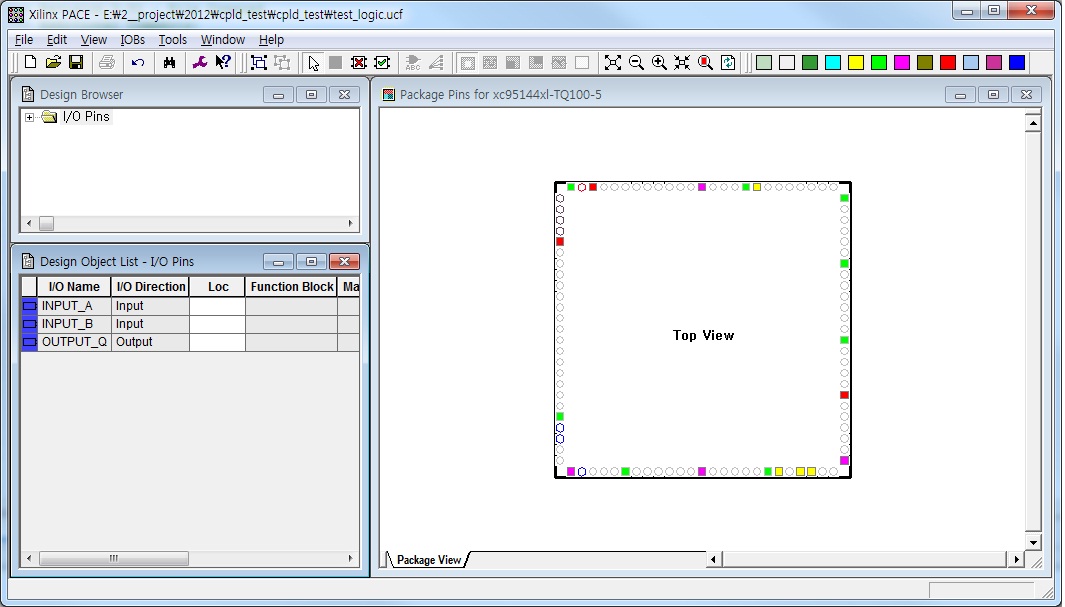

16. pin 매핑

다시 14번 항목으로 돌아가 실행 해 보면 아래와 같이 선언한 pin 과 실제 chip 의 이미지가 나옵니다.

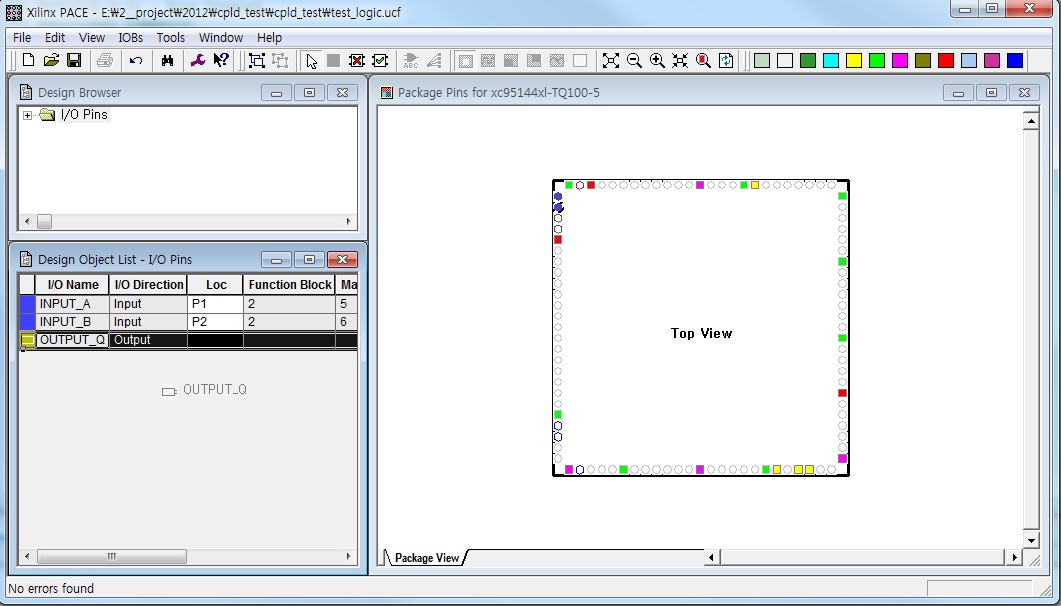

16. pin 위치 선택

선언한 pin 을 마우스로 드래그해 우측의 chip 이미지의 원하는 pin 번호에 올려 놓습니다.

이미지에 pin 번호가 나오지 않아 좀 답답 하지만, 걱정 하지 않아도 됩니다.

왜냐면 나중에 소스에서 수정이 가능 하기 때문이지요.

일단은 그 매핑 소스를 만들어야 하기 때문에 그냥 대충 아무데나 한두개 핀만 올려 놓습니다.

저장을 누릅니다.

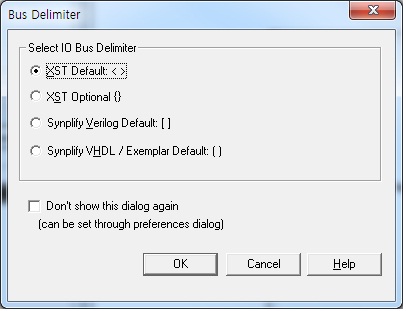

17.아래 이미지대로 xst default 를 선택 하고 ok 를 누릅니다.

pin 매핑 화면을 닫아 줍니다.

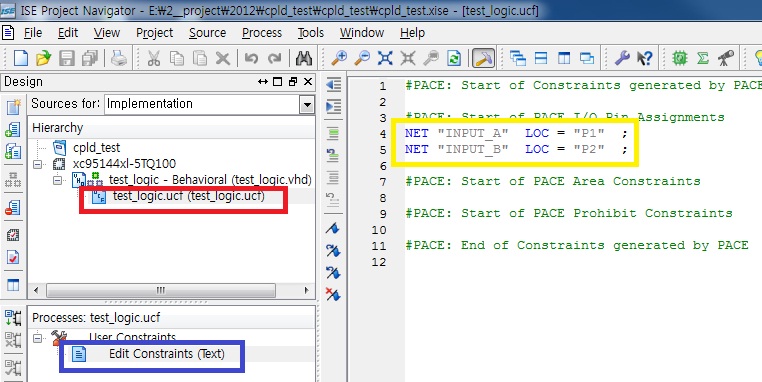

18. 소스 내용 확인

생성한 pin매칭 파일은 확장자가 ucf 입니다. 이 파일 역시 프로젝트 생성 폴더내에 있으며 다른 에디터로 직접 수정이 가능 합니다.

그 파일을 열기 위해서는 아래 그림의 붉은색 네모박스처럼 파일을 선택 하면 나오는 아래 파란 네모를 더블클릭 해 주어야 합니다.

vhd 파일은 그냥 아래 그림의 붉은 네모 상자의 위에 있는 파일을 더블클릭하면 열리는 것과 다릅니다.

여튼 ucf 파일을 열어보면 아까 드래그해서 매칭시킨 핀들이 정의 돼 있음을 확인 할 수 있습니다.

여기서 p1, p2 는 사용할 chip 의 1번핀, 2 번핀을 의미 합니다.

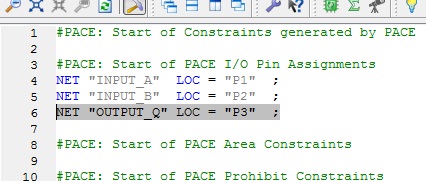

19. 나머지 핀 정의 하기

아까 두개의 입력만 매칭시켰기 때문에 나머지 핀은 직접 코드를 추가해 수정해 줍니다.

사실 실제 사용할 핀의 수가 약 70개에 가까운데 이것들을 일일이 번호를 봐가며 드래그 한다는건 짜증나는 일이 아닐 수 없습니다. 그렇기 때문에 직접 소스를 열어 수정 하는 것이 편하다고 생각 합니다.

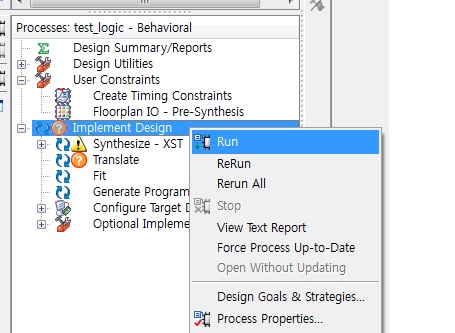

20. 컴파일 하기

이상태로 컴파일을 하면 pin 만 정의 한상태 이기 때문에 컴파일 과정이 전부 진행 되지 않고 중간에 멈추며, 최종 결과파일도

생성되지 않습니다. 이번 강좌에서는 소스코드나 문법에 대해 설명 하지 않기 때문에 이미 만들어진 코드로 컴파일 하는 것만

설명 하겠습니다.

아래 그림과 같이 Implement Design 을 선택 하고 우측 마우스를 눌러 run 을 선택하면 컴파일이 시작 됩니다.

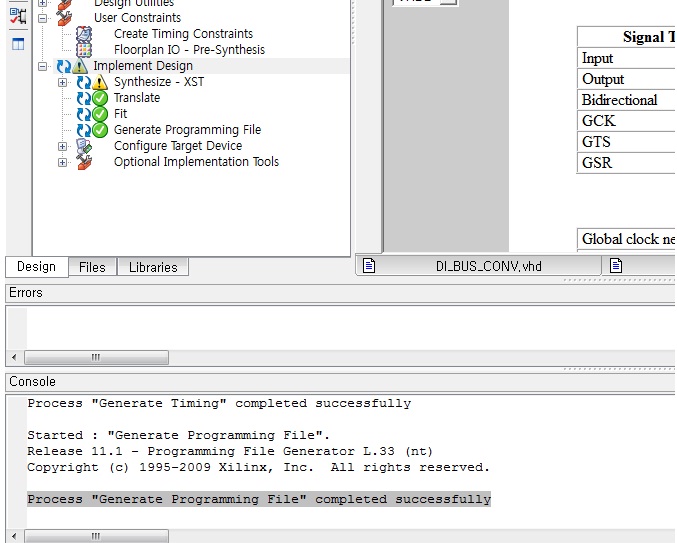

20. 컴파일 완료 확인

컴파일이 완료되면 아래 그림과 같이 파란색으로 체크 되며, 아래 메시지에 완료가 됐다고 나옵니다.

21. 최종 결과 파일

컴파일된 파일의 확장자는 jed 파일이며, 이또한 프로젝트 생성 폴더에 만들어집니다.

![]()

아.. 그림 파일이 25 개 밖에 안올라가네요. jtag 으로 라이팅하는 부분은 다음주에 해야겠습니다.

- 0.jpg (20.6KB)(260)

- 1.jpg (71.1KB)(207)

- 2.jpg (100.9KB)(178)

- 3.jpg (58.0KB)(179)

- 4.jpg (60.1KB)(181)

- 5.jpg (88.9KB)(176)

- 6.jpg (159.7KB)(193)

- 7.jpg (39.8KB)(149)

- 8.jpg (60.9KB)(180)

- 9.jpg (70.2KB)(163)

- 10.jpg (61.1KB)(151)

- 11.jpg (124.9KB)(170)

- 12.jpg (104.1KB)(165)

- 13.jpg (184.6KB)(189)

- 14.jpg (27.9KB)(193)

- 15.jpg (44.6KB)(160)

- 16.jpg (155.8KB)(173)

- 17.jpg (131.9KB)(170)

- 18.jpg (134.1KB)(176)

- 19.jpg (32.6KB)(191)

- 20.jpg (108.7KB)(163)

- 22.jpg (36.6KB)(170)

- 23.jpg (53.7KB)(172)

- 24.jpg (96.1KB)(178)

- 25.jpg (13.8KB)(209)