강좌 & 팁

멀티 코어가 나오면서 ARM 역시 그 복잡도가 직관적 이해를 할수 있는

범위를 벗어나기 시작한 것 같습니다.

흔히 말하는 coherent 문제는 이제 새롭지도 않습니다.

어떻게 하면 SCU 라는 녀석과 coherent 를 잘 이해할까? 하면서

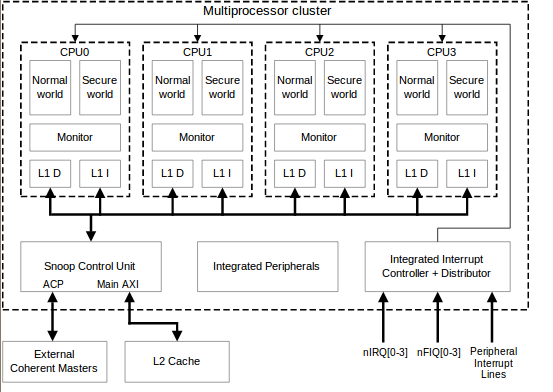

이미지 검색을 하다가 딱 이거다! 하는 그림이 있는데 역시 arm infocenter 에 있는 그림이군요.

캡쳐를 했는데 음.. 어쨋든 한번 보시죠..

coherent 문제는 싱글 코어에서는 심심찮게 나타나지만 멀티코어에서는 아주 심각한 문제로 등장합니다.

그 이유는 바로 각각의 cpu 에서 독립적인 mmu table 을 갖고 있고 L1 cache 를 각각 갖고 있습니다.

풀어서 얘기하면 각각의 cpu 들은 독립적으로 mmu table 과 data, instruction cache 를 갖고 동작합니다.

당연히 다른 cpu 와 "독립" 적으로 움직입니다.

이에 따라서 동일한 메모리에 대한 접근이 일어날때 cache 에 의해서 메모리에 있는 값과는

다른 값으로 인식할 가능성이 높아진 것입니다.

여기에 scu 의 역할이 있습니다.

scu 에서는 I-cache 에 대한 역할은 하지 않습니다.

D-cache 에 대한 coherent 만을 다루고 있습니다.

또 AXI 버스를 통해서 L2 cache 가 memroy 에 접근하게 되므로 이에 대한 초기화를 담당합니다.

또한가지 중요한 역할은 여러개의 cpu 에서 L2 cache 에 접근할때 이에 대한 arbitration 을 관리합니다.

이 녀석은 이해하기도 어려웠는데 설명하기도 어렵군요.

이런 글을 여러개 읽다 보면 더 잘 이해가 가실겁니다.