하드웨어

글 수 321

2014.04.18 09:55:03 (*.134.169.166)

18459

cpu 와 같은 칩들은 대부분 i/o 전원과 core 전원이 분리되어 있습니다.

그래서 이런 칩들을 이용한 회로를 설계 할 때는 여러개의 전원을 공급해 주게 되는데요

정말 복잡하게 많은 전원을 공급 하는 경우 pmic 를 사용 하지만, 간혹 2~3 개 정도의 전원을

공급해야 하는 칩이라면 각각의 전원을 직접 만들어 공급 하곤 합니다.

그런데. 문제가 있습니다.

이런 여러개의 전원의 공급 순서가 있다는 겁니다.

물론 그냥 대충 넣으면 되는 칩도 있겠으나, core 저원과 i/o 전원의 경우 대부분 공급해 주어야 하는 순서가

정해져 있습니다.

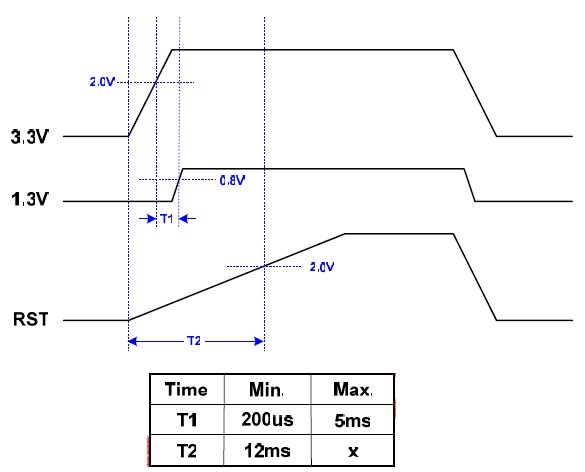

이번에 사용한 어떤 칩은 아래 그램과 같은 전원 공급 순서를 요구 했습니다.

이 chip 은 i/o 전원을 3.3v 로 사용 하고 core 저원을 1.3v 로 사용 합니다.

타이밍도를 보면, 3.3v 가 먼저 공급되고, 200uSec 이후 1.3v 가 공급되고 3.3v 가 입력된 12msec 이후 reset 이 발생되어야

정상 동작된다는 조건이 있음을 알 수 있습니다.

이런 티이밍들을 pmic 를 사용 하면 좋겠으나 ldo 등을 사용 한다면 어떻게 200uSec ~ 5msec 를 맞출 까요?

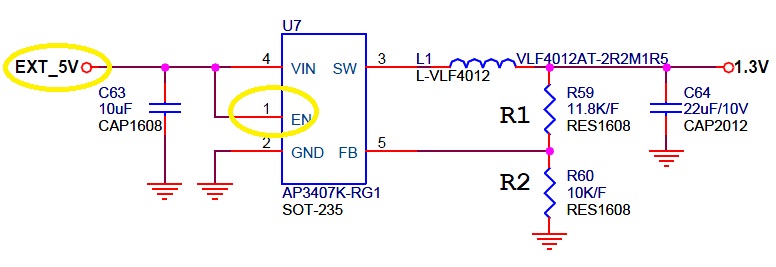

바로 enable 신호에 cap 을 달아서 제어를 할 수 있습니다.

en 신호에 cap 을 연결해 충전되는 시간동안 1.3v 출력 시간을 딜레시 시킬 수 있습니다.