하드웨어

안녕하세요? 오늘은 날씨가 선선하고 산뜻한 기분 좋은 날씨였던 것 같습니다. ^^

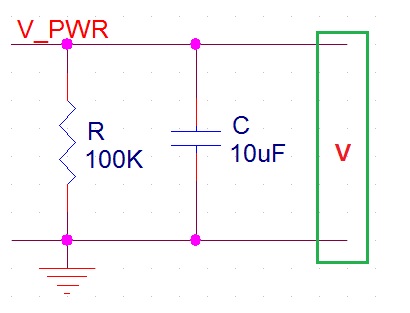

이런 기분 좋은 하루와 함께, 오늘은 다소 기초적이지만 회로 설계에 있어 아주 유용한 R과 C를 조합한 응용 회로에 대하여

알아보겠습니다. 그중 첫번째는 저항과 캐패시터를 한번 병렬(Parallel)로 놓아 보겠습니다.

R과 C가 병렬로 구성되어진 회로에선 어떤 구성이 되어질까요??

이런 구조에서 양단에 전압이 걸리게 되면 저항을 통하여 전류가 약간 흐를뿐 아니라 캐피시터 쪽으로 충전에너지도 생기게 됩니다.

따라서 전압이 사라진 상태가 되면 캐패시터는 구성된 저항을 통하여 가지고 있는 에너지를 방전하게 되지요.

저항이 전류의 흐르는 속도를 제한해 줌으로 인하여, 캐패시터의 방전되는 전압 속도를 제한하는 셈이 되게 됩니다

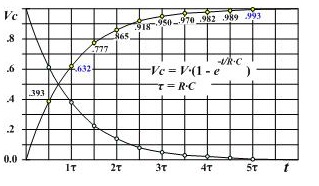

이런 식으로 우리는 전압의 방전되는 곡선을 확인할 수 있는데요, RC회로에서는 출력 전압이 서서히 떨어지다가, 출력 전압이

최대 입력 전압의 37%의 지점을 지나게 되는 Time Constant를 만나게 됩니다. 이 지점을 우리는 "시정수"라고 말하지요.

단순히 말하면 R과 C를 곱한 값을 말하게 됩니다. ^^

그럼 위의 회로를 예로 들어 볼까요? R의 값을 100KΩ으로, C의 값을 10uF으로 걸어주게 되었으니, T=R*C[Sec]로

우리는 1Sec의 방전되는 시정수 결과를 가질수 있습니다.

이제 다음 시간에는 우리가 가장 많이 유용하게 사용하는 R과 C의 직렬 연결구조, 그리고 C와 L의 특성을 이용한 전원 노이즈

개선 방법, 그 응용사례 등에 대하여 한번 알아보도록 하겠습니다. ^^